### **UNIT I - MOS TRANSISTOR PRINCIPLE**

NMOS and PMOS transistors, Process parameters for MOS and CMOS, Electrical properties of CMOS circuits and device modeling, Scaling principles and fundamental limits, CMOS inverter scaling, propagation delays, Stick diagram, Layout diagrams.

### 1.1: INTRODUCTION: (VLSI)

In 1958, Jack Kilby built the first integrated circuit flip-flop at Texas Instruments.

Bell Labs developed the bipolar junction transistor. Bipolar transistors were more reliable, less noisy and more power-efficient.

In 1960s, Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) began to enter in the production.

MOSFETs offer the compelling advantage that, they draw almost zero control current while idle.

They come in two flavors: nMOS and pMOS, using n-type and p-type silicon respectively.

In 1963, Frank Wanlass at Fairchild described the first logic gates using MOSFETs.

Fairchild's gates used both nMOS and pMOS transistors, naming as Complementary Metal Oxide Semiconductor (CMOS).

Power consumption became a major issue in the 1980s as hundreds of thousands of transistors were integrated onto a single die.

CMOS processes were widely adopted and replaced nMOS and bipolar processes for all digital logic applications.

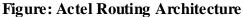

In 1965, Gordon Moore observed that plotting the number of transistors that can be most economically manufactured on a chip gives a straight line on a semi logarithmic scale.

The level of integration of chips is classified as

- Small Scale Integration (SSI)

- Medium Scale Integration (MSI)

- Large Scale Integration (LSI)

- Very Large Scale Integration (VLSI)

- Ultra Large Scale Integration (ULSI)

#### **Small scale Integration:**

Small-Scale Integration (SSI) circuits have less than 10 gates. Example: 7404 inverter.

#### Medium scale Integration:

Medium-Scale Integration (MSI) circuits have up to 1000 gates. Example: 74161 counter.

#### Large scale Integration:

*Large-Scale Integration* (LSI) circuits have up to 10,000 gates. Example: 8-bit microprocessor (8085).

$\checkmark$

Very large scale Integration (VLSI) with gates counting up to lakhs. Example: 16-bit microprocessor (8086).

The feature size of a CMOS manufacturing process refers to the minimum dimension of a transistor that can be reliably built.

### Ultra large scale Integration:

Ultra Large-Scale Integration (ULSI) is the process of integrating millions of transistors on a single silicon semiconductor microchip.

### 1.2: nMOS and pMOS transistor

Explain the basic concept of nMOS and pMOS transistor with relevant symbol.

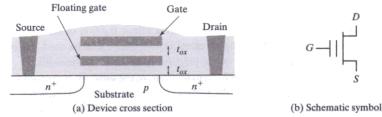

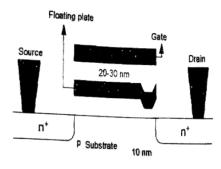

A Metal-Oxide-Semiconductor (MOS) structure is created by superimposing layers of conducting and insulating materials.

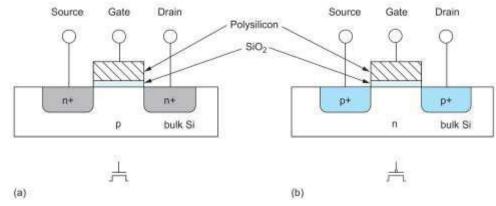

CMOS technology provides two types of transistors. They are n-type transistor (nMOS) and p-type transistor (pMOS).

As transistor operation is controlled by electric fields, the devices are also called Metal Oxide Semiconductor Field Effect Transistors (MOSFETs).

$\checkmark$

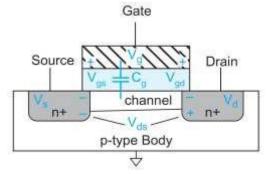

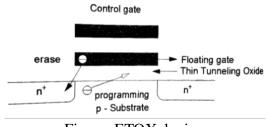

The transistor consists of a stack of the conducting gate, an insulating layer of silicon dioxide (SiO2) and the silicon wafer, also called as substrate, body or bulk.

A pMOS transistor consists of p-type source and drain region with an n-type body.

An nMOS transistor consists of n-type source and drain region with a p-type body.

Figure 1: (a) n-MOS transistor (b) p-MOS transistor

### nMOS Transistor:

In an nMOS transistor, the body is grounded and the p-n junction of the source and drain to body are reverse-biased.

- As the gate is grounded, no current flows through junction. Hence, the transistor is OFF.

- If the gate voltage is raised, it creates an electric field, that start to attract free electrons to the underside of the Si–SiO<sub>2</sub> interface.

- If the voltage is raised more, a thin region under the gate called the channel is inverted.

Since a conducting path of electron carriers is formed from source to drain, current starts to flow. So, the transistor is said to be ON.

### pMOS Transistor:

For a pMOS transistor, the body is held at a positive voltage.

When the gate terminal has a positive voltage, the source and drain junctions are reverse-biased and no current flows. So, the transistor is said to OFF.

When the gate voltage is lowered, positive charges are attracted to the underside of the Si– SiO2 interface.

When a sufficient low gate voltage is applied, the channel inverts and a conducting path of positive carriers is formed from source to drain, which makes the transistor ON.

### NOTE:

- The symbol for the pMOS transistor has a bubble on the gate, indicating that the transistor behavior is opposite to nMOS.

- When the gate of an nMOS transistor is 1, the transistor is ON. When the gate is 0, the nMOS transistor is OFF.

- A pMOS transistor is ON when the gate is low(0) and OFF when the gate is high(1).

### 1.3: Modes of MOS TRANSISTOR

# Explain the accumulation mode, depletion layer and inversion layer of MOS transistor with diagram.

- The MOS transistor is a majority-carrier device, in which the current in a conducting channel is controlled by gate voltage.

- In an nMOS transistor, the majority carriers are electrons.

- In a pMOS transistor, the majority carriers are holes.

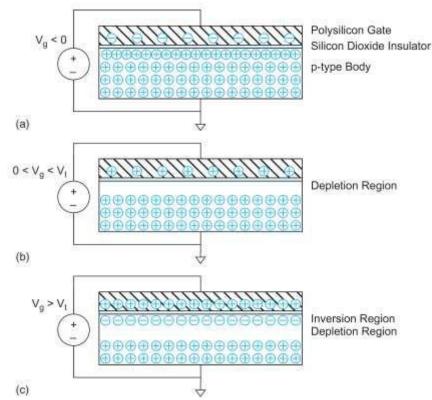

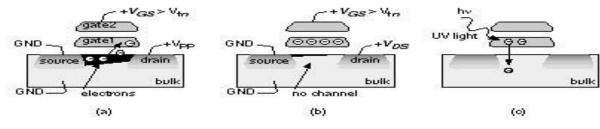

- Figure 2 shows a simple MOS structure. The top layer of the structure is a good conductor called the gate.

- $\checkmark$

Transistor gate is polysilicon, i.e., silicon formed from many small crystals. The middle layer is a very thin insulating film of SiO<sub>2</sub>, called the gate oxide. The bottom layer is the doped silicon body.

- $\checkmark$

- The figure 2 shows a p-type body, in which the carriers are holes. The body is grounded and voltage is applied to the gate.

The gate oxide is a good insulator, so almost zero current flows from the gate to the body.

#### Accumulation mode:

- In Figure 2(a), when a negative voltage is applied to the gate, negative charges are formed on the gate.

- The positively charged holes are attracted to the region under the gate. This is called the accumulation mode.

### **Depletion mode:**

In Figure 2(b), when a small positive voltage is applied to the gate, positive charges are formed on the gate.

The holes in the body are repelled from the region directly under the gate, resulting in a depletion region forming below the gate.

### Inversion layer:

$\checkmark$

In Figure 2(c), when a higher positive potential greater than threshold voltage  $(V_t)$  is applied, more positive charges are attracted to the gate.

The holes are repelled and some free electrons in the body are attracted to the region under the gate. This conductive layer of electrons in the p-type body is called the inversion layer.

The threshold voltage depends on the number of dopants in the body and the thickness tox of the oxide.

Figure 2: MOS structure demonstrating (a) accumulation, (b) depletion, and (c) inversion layer

### 1.4: Operating regions of MOS transistor:

Explain the three different types of modes of operation of nMOS transistor. (or) Discuss the cutoff, linear and saturation region operation of MOS transistor. (Nov 2009)

The MOS transistor operates in cutoff region, linear region and saturation region.

### **Cutoff region:**

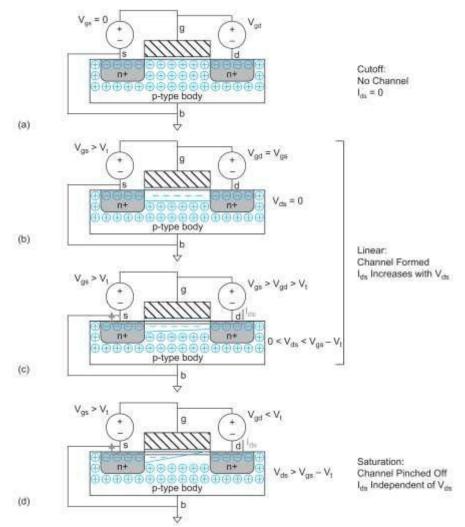

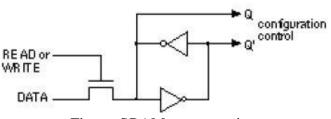

In Figure 3(a), the gate-to-source voltage ( $V_{gs}$ ) is less than the threshold voltage ( $V_t$ ) and source is grounded.

Junctions between the body and the source or drain are reverse biased, so no current flows. Thus, the transistor is said to be OFF and this mode of operation is called cutoff.

If  $V_{gs} < V_t$ , the transistor is cutoff (OFF).

### **Linear Region:**

√

In Figure 3(b), the gate voltage is greater than the threshold voltage.

An inversion region of electrons, called the channel connects the source and drain, creating a conductive path and making the transistor ON.

If  $V_{gs} > V_t$ , the transistor turns ON. If  $V_{ds}$  is small, the transistor acts as a linear resistor, in which the current flow is proportional to  $V_{ds}$ .

The number of carriers and the conductivity increases, with the gate voltage.

### Figure 3: nMOS transistor demonstrating cutoff, linear, and saturation regions of operation

The voltage between drain and source is  $V_{ds} = V_{gs} - V_{gd}$ . If  $V_{ds} = 0$  (i.e.,  $V_{gs} = V_{gd}$ ), there is no electric field to push current from drain to source.

$\checkmark$

~

When a small positive voltage Vds is applied to the drain (Figure 3(c)), current Ids flows through the channel from drain to source.

This mode of operation is termed as linear, resistive, triode, nonsaturated, or unsaturated. **Saturation region:**

The current increases with increase in both the drain voltage and gate voltage.

If  $V_{ds}$  becomes sufficiently large that  $V_{gd} < V_t$ , the channel is no longer inverted near the drain and becomes pinched off (Figure 3(d)).

- As electrons reach the end of the channel, they are injected into the depletion region near the drain and accelerated toward the drain.

- Above this drain voltage, current Ids are controlled only by the gate voltage. This mode is called saturation.

If  $V_{gs} > V_t$  and  $V_{ds}$  is large, the transistor acts as a current source, in which the current flow becomes independent of  $V_{ds}$ .

### Explain the three different types of modes of operation of pMOS transistor.

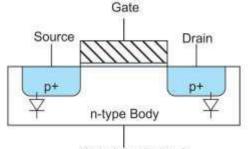

- The pMOS transistor in Figure 4 operates in just the opposite fashion. The n-type body is tied to high potential, junctions of p-type source and drains are normally reverse-biased.

- When the gate has high potential, no current flows between drain and source.

- When the gate voltage is lowered by a threshold  $V_t$ , holes are attracted to form a p-type channel beneath the gate, allowing current to flow between drain and source.

### Body (usually V<sub>DD</sub>)

Figure 4: pMOS transistor

**1.5: IDEAL I-V CHARACTERISTICS OF MOS TRANSISTOR**

- \*\* Explain in detail about the ideal I-V characteristics of a NMOS and PMOS device. (MAY 2013) ••• Discuss in detail with necessary equations the operation of MOSFET and its current-voltage characteristics. (April/May 2011, May 2016). \* Derive drain current of MOS device in different operating regions. (Nov/Dec 2014)(May/June 2013) (Nov 2012, Nov 2016) \* Explain in detail about the ideal I-V characteristics and non-ideal I-V characteristics of a NMOS and PMOS device. (May/June 2013) \*\* Derive expressions for the drain-to-source current in the nonsaturated and saturated regions of operation of an nMOS transistor. (Nov 2007, Nov 2008) MOS transistor has three regions of operation: • Cutoff or subthreshold region

- Linear region

- Saturation region

- The current through an OFF transistor is zero. When a transistor turns ON  $(V_{gs} > V_t)$ , the gate attract electrons to form a channel.

- Current is measured from the amount of charge in the channel.

The charge on each plate of a capacitor is Q = CV. Thus, the charge in the channel Q-thannel is

$$Q_{\text{channel}} = C_g (V_{gc} - V_t)$$

where  $C_g$  : Capacitance of the gate to the channel

$V_{gc}$  -  $V_t$ : A mount of voltage attracting charge to the channel.

If the source is at  $V_s$  and the drain is at  $V_d$ ,

Average channel voltage is  $V_c = (V_s + V_d)/2 = V_s + V_{ds}/2$ .

Gate and channel voltage  $V_{gc}$  is  $V_g - V_c = V_{gs} - V_{ds}/2$ ,

Figure 5: Average gate to channel voltage

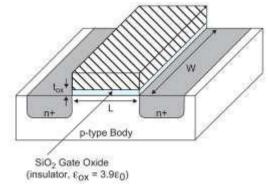

If the gate has length L and width W and the oxide thickness is tox, as shown in Figure 6, Then the capacitance  $C_g$  is

Where,

Permittivity of SiO2 is  $k_{\text{ox}} = 3.9$  times as great.

The  $\varepsilon_{0x}/t_{0x}$  term is called as  $C_{0x}$ . Capacitance ( $C_{0x}$ ) is a per unit area of the gate 0 xide.

Figure 6: Transistor dimensions

Average velocity (v) of carrier is proportional to the lateral electric field (field between source and drain). The constant of proportionality  $\mu$  is called the mobility.

$$v = \mu E$$

-----(2)

The electric field E is the voltage difference between drain and source ( $V_{ds}$ ) divided by the channel length (L).

$$E = \frac{V}{L} - \dots - (3)$$

The time required for carriers to cross the channel is L divided by v.

The current between source and drain is the total amount of charge in the channel divided by the time required to cross.

EC6601-VLSI DESIGN

UNIT-I

$$\begin{split} I_{dt} &= \frac{Q_{\text{channel}}}{L/\upsilon} \\ &= \mu C_{\text{ox}} \frac{W}{L} \Big( V_{gr} - V_t - V_{ds} / 2 \Big) V_{dt} \\ &= \beta \Big( V_{GT} - V_{ds} / 2 \Big) V_{dt} \end{split}$$

where

Equation (4) is called linear or resistive, because when  $V_{ds} \ll V_{GT}$ ,  $I_{ds}$  increases linearly with  $V_{ds}$ , like an ideal resistor.

k' is the k prime, k' =  $\mu C_{ox}$ .

If  $V_{ds} > V_{dsat} = V_{GT}$ , the channel is no longer inverted in the drain region. Channel is pinched off.

Beyond this point (called the drain saturation voltage), increasing the drain voltage has no further effect on current.

Substituting  $V_{ds} = V_{dsat}$  in Eq (4), we can find an expression for the saturation current (Ids) that is independent of  $V_{ds}$ .

$$I = \frac{\beta}{2} V^2$$

(5)

This expression is valid for  $V_{gs} > V_t$  and  $V_{ds} > V_{dsat}$ .

$\checkmark$

\*

÷

$\checkmark$

Summarizes the current in the three regions:

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{t} & \text{Cutoff} \\ \beta (V_{GT} - V_{ds}/2) V_{ds} & V_{ds} < V_{\text{dsat}} & \text{Linear} \\ \frac{\beta}{2} V_{GT}^{2} & V_{ds} > V_{\text{dsat}} & \text{Saturation} \end{cases}$$

<u>1.6: C – V CHARACTERISTICS OF MOS TRANSISTOR (AC characteristics)</u>

Discuss the CV characteristics of the CMOS. (Nov 2012, May 2014, Nov 2015, Nov 2016)

Explain the electrical properties CMOS. (Nov 2017)

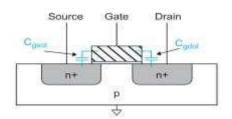

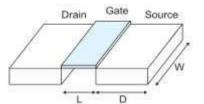

Each terminal of an MOS transistor has capacitance to the other terminals. Capacitances are nonlinear and voltage dependent (C-V).

#### SIMPLE MOS CAPACITANCES MODEL:

The gate of an MOS transistor is a good capacitor. Its capacitance is necessary to attract charge to invert the channel, so high gate capacitance is required to obtain high *Ids*.

The gate capacitor can be viewed as a parallel plate capacitor with the gate on top, channel on bottom and the thin oxide dielectric between.

The capacitance is  $C_g = C_{0x} WL$ . -----(1)

$C_g = C_{permicron} W -----(2)$

Where C<sub>permicron</sub> = C<sub>ox</sub> L =

$$\frac{\mathcal{E}_{ox}}{t}$$

L

In addition to the gate, the source and drain also have capacitances. These capacitances are called parasitic capacitors.

The source and drain capacitances arise from the p-n junctions between the source or drain diffusion and the body. These capacitances are called diffusion capacitance  $C_{sb}$  and  $C_{db}$ .

The depletion region acts as an insulator between the conducting p- and n-type regions, creating capacitance across the junction.

- The capacitance of junctions depends on the area and perimeter of the source and drain diffusion, the depth of the diffusion, the doping levels and the voltage.

- As diffusion has both high capacitance and high resistance, it is generally made as small as possible in the layout.

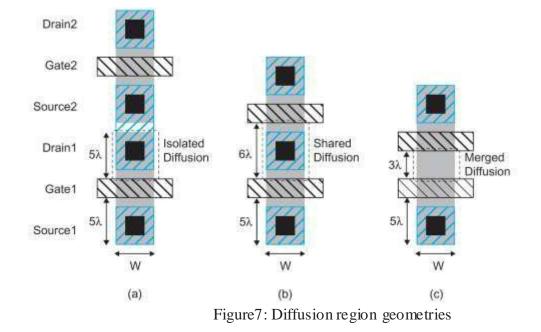

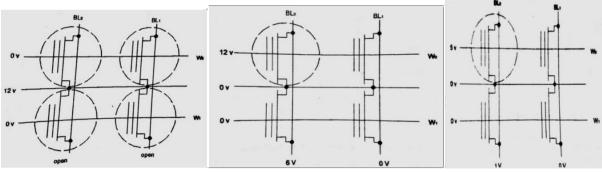

- Three types of diffusion regions are illustrated by the two series transistors in Figure 7.

- In Figure 7(a), each source and drain has its own isolated region of contacted diffusion.

- In Figure 7(b), the drain of the bottom transistor and source of the top transistor form a shared contacted diffusion region.

- In Figure 7(c), the source and drain are merged into an uncontacted region.

#### DETAILED MOS GATE CAPACITANCE MODEL:

- $\checkmark$

- MOS gate places above the channel and may partially overlap the source and drain diffusion areas.

- The gate capacitance has two components, (i) the intrinsic capacitance  $C_{gc}$  (over the channel) and (ii) the overlap capacitances  $C_{gol}$  (to the source and drain).

- The intrinsic capacitance was approximated as a simple parallel plate with capacitance

$C_0 = WLC_{\text{ox.}}$

The intrinsic capacitance has three components representing the different terminals connected to the bottom plate are  $C_{gb}$  (gate-to-body),  $C_{gs}$  (gate-to-source), and  $C_{gd}$  (gate-to-drain).

The behavior in three regions (Cutoff, Linear and Saturation) can be approximated as shown in Table 1.

#### EC6601-VLSI DESIGN

UNIT-I

| Parameter                        | Gutoff     | Linear  | Saturation |

|----------------------------------|------------|---------|------------|

| $C_{g^{b}}$                      | $\leq C_0$ | 0       | 0          |

| $C_{p}$                          | 0          | $C_0/2$ | 2/3 Co     |

| C <sub>kd</sub>                  | 0          | $C_0/2$ | 0          |

| $C_g = C_{gi} + C_{gi} + C_{gi}$ | $C_0$      | $C_0$   | 2/3 Co     |

Table1: Approximation for intrinsic MOS gate capacitance

#### DETAILED MOS DIFFUSION CAPACITANCE MODEL:

The capacitance depends on both the area AS and sidewall perimeter PS of the source diffusion region. The area is AS = WD.

The perimeter is PS = 2W + 2D.

Figure 9: Diffusion region geometry

The total source parasitic capacitance is  $C_{sb} = AS * C_{jbs} + PS * C_{jbssw}$

Where, Cjbs - Capacitance of the junction between the body and the bottom of the source

Cjbssw - Capacitance of the junction between the body and the side walls of the source

In summary, MOS transistor can be viewed as a four-terminal device with capacitances between each terminal pair, as shown in Figure 10.

Figure 10: Capacitance of a MOS Transistor

The gate capacitance includes an intrinsic component and overlap terms with the source and drain. The source and drain have parasitic diffusion capacitance to the body.

#### **1.7: DC TRANSFER CHARACTERISTICS**

Explain the DC transfer characteristic of CMOS inverter.[APRIL-2015, Nov 2015]

Draw and explain the DC and transfer characteristics of a CMOS inverter with necessary conditions for the different regions of operation. (Nov/Dec 2011) (Nov/Dec 2012) (May/June 2013) (April/May 2012) (May/June 2014) (Nov/Dec 2013) (May 2016, May 2017, Nov 2008)

Explain the CMOS inverter DC characteristics. (Nov 2007, Nov 2009)

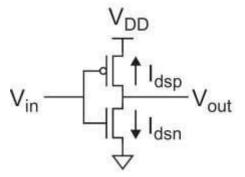

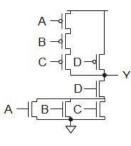

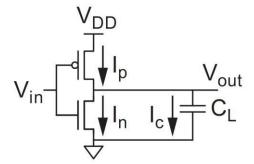

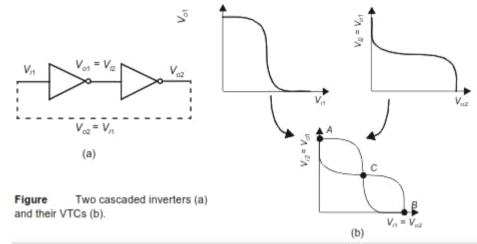

The DC transfer characteristics of a circuit relate the output voltage to the input voltage.

- (i) Static CMOS inverter DC Characteristics:

- $\checkmark$

$\checkmark$

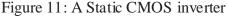

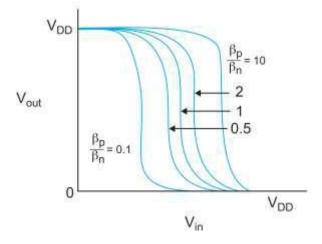

The DC transfer function (Vout Vs. Vin) for the static CMOS inverter shown in Figure 11.

Table 2, shows various regions of operation for the n and p transistors.

In this table,  $V_{tn}$  is the threshold voltage of the n-channel device, and  $V_{tp}$  is the threshold voltage of the p-channel device.  $V_{tp}$  is negative.

The equations are given both in terms of  $V_{gs} / V_{ds}$  and  $V_{in} / V_{out}$ .

As the source of the nMOS transistor is grounded,  $V_{gsn} = V_{in}$  and  $V_{dsn} = V_{out}$ .

As the source of the pMOS transistor is tied to VDD,  $V_{gsp} = V_{in} - V_{DD}$  and  $V_{dsp} = V_{out} - V_{DD}$ .

|      | Cutoff                         | Linear                              | Saturated                           |

|------|--------------------------------|-------------------------------------|-------------------------------------|

| nMOS | $V_{gsn} < V_{tn}$             | $V_{gsn} > V_{tn}$                  | $V_{gsn} > V_{tn}$                  |

|      | $V_{\rm in} < V_{tn}$          | $V_{\rm in} > V_m$                  | $V_{\rm in} > V_{tn}$               |

|      |                                | $V_{dsn} < V_{gsn} - V_{tn}$        | $V_{dsn} > V_{gsn} - V_{tn}$        |

|      |                                | $V_{\rm out} < V_{\rm in} - V_{m}$  | $V_{\rm out} > V_{\rm in} - V_{tn}$ |

| pMOS | $V_{gip} > V_{tp}$             | $V_{gsp} < V_{tp}$                  | $V_{gip} < V_{tp}$                  |

|      | $V_{\rm in} > V_{tp} + V_{DD}$ | $V_{\rm in} < V_{tp} + V_{DD}$      | $V_{\rm in} < V_{ip} + V_{DD}$      |

|      |                                | $V_{dsp} > V_{gsp} - V_{tp}$        | $V_{dsp} < V_{gsp} - V_{tp}$        |

|      |                                | $V_{\rm out} > V_{\rm in} - V_{tp}$ | $V_{\rm out} < V_{\rm in} - V_{tp}$ |

Table 2: Relationships between voltages for the three regions of operation of a CMOS inverter

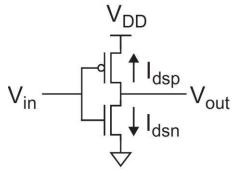

Figure 12(a), shows  $I_{dsn}$  and  $I_{dsp}$  in terms of  $V_{dsn}$  and  $V_{dsp}$  for various values of  $V_{gsn}$  and  $V_{gsp}$ .

- Figure 12(b), shows the same plot of  $I_{dsn}$  and  $|I_{dsp}|$  in terms of  $V_{out}$  for various values of  $V_{in}$ .

- Operating points are plotted on V<sub>out</sub> vs. V<sub>in</sub> axes in Figure 12(c) to show the inverter DC transfer characteristics.

- The supply current  $I_{DD} = I_{dsn} = |I_{dsp}|$  is plotted against  $V_{in}$  in Figure 13(d) showing that both transistors are momentarily ON as  $V_{in}$ .

The operation of the CMOS inverter can be divided into five regions as indicated on figure 12(c).

Figure 12: CMOS inverter DC characteristic

The state of each transistor in each region is shown in Table 3.

| Region | Condition                                                   | p-device  | n-device  | Output                   |

|--------|-------------------------------------------------------------|-----------|-----------|--------------------------|

| А      | $0 \le V_{in} < V_{tn}$                                     | linear    | cutoff    | $V_{\rm out} = V_{DD}$   |

| В      | $V_{tn} \leq V_{\rm in} < V_{DD}/2$                         | linear    | saturated | $V_{\rm out} > V_{DD}/2$ |

| С      | $V_{\rm in} = V_{DD}/2$                                     | saturated | saturated | Vout drops sharply       |

| D      | $V_{DD}/2 < V_{\rm in} \leq V_{DD} - \left  V_{tp} \right $ | saturated | linear    | $V_{\rm out} < V_{DD}/2$ |

| Е      | $V_{\rm in} > V_{DD} -  V_{tp} $                            | cutoff    | linear    | $V_{\rm out} = 0$        |

#### Table 3: Summary of CMOS inverter operation.

- In region A, the nMOS transistor is OFF and the pMOS transistor pulls the output to VDD.

- In region *B*, the nMOS transistor starts to turn ON. It is pulling the output down.

- In region *C*, both transistors are in saturation.

- In region *D*, the pMOS transistor is partially ON.

In region *E*, PMOS is completely OFF, making the nMOS transistor to pull the output down to GND.

#### EC6601-VLSI DESIGN

#### UNIT-I

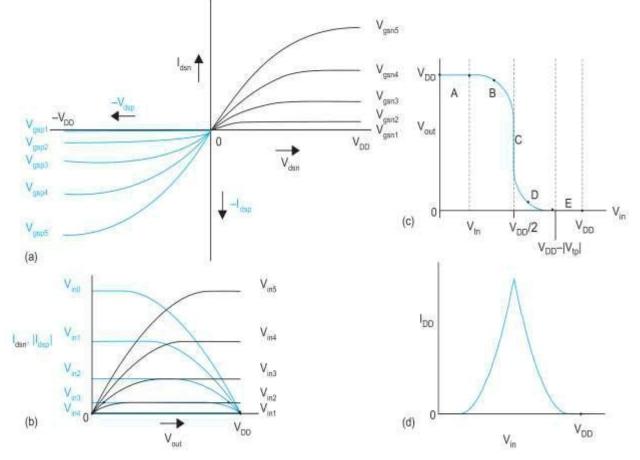

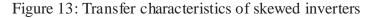

#### (ii) Beta ratio Effects:

For  $\beta_p = \beta_n$ , the inverter threshold voltage V<sub>inv</sub> is V<sub>DD</sub>/2.

It allows a capacitive load to charge and discharge in equal times by providing equal current source and equal sink capabilities.

Inverter with different beta ratios  $r = \beta_p / \beta_n$  is called skewed inverter.

If r > 1, the inverter is HI-skewed. If r < 1, the inverter is LO-skewed. If r = 1, the inverter has normal skew or is unskewed.

Figure 13, shows the impact of skewing the beta ratio on the DC transfer characteristics.

$\checkmark$  As the beta ratio is changed, the switching threshold is varied.

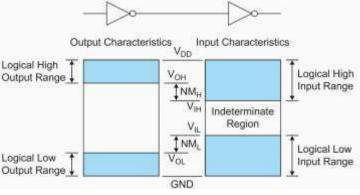

### Derive the noise margins for a CMOS inverter. (May 2010, Nov 2016) (iii) Noise Margins:

Noise margin (Noise immunity) is related to the DC voltage characteristics.

Noise Margin allows determining the allowable noise voltage on the input of a gate, so that the output will not be corrupted.

Two parameters of the noise margin are LOW noise margin (NML), and the HIGH noise margin (NMH).

Figure 14: Noise Margin Definitions

NML is defined as the difference in maximum LOW input voltage  $V_{IL}$  and the maximum LOW output voltage  $V_{OL}$ .  $NM_L = V_{IL} - V_{OL}$

The value of NMH is the difference between the minimum HIGH output voltage VOH and the minimum HIGH input voltage VIH. i.e., NMH = VOH - VIH

Inputs between VIL and VIH are said to be in the indeterminate region or forbidden zone.

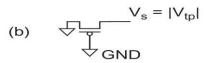

### (iv) Pass Transistor DC Characteristics:

The nMOS transistors pass 0's well but 1's poorly. Figure 15(a), shows an nMOS transistor with the gate and drain tied to VDD.

Initially at Vs = 0.  $V_{gs} > V_{tn}$ , so the transistor is ON and current flow.

Therefore, nMOS transistors attempting to pass a 1 never pull the source above  $VDD - V_{tn}$ . This loss is called a threshold drop.

The pMOS transistors pass 1's well but 0's poorly.

If the pMOS source drops below  $|V_{tp}|$ , the transistor cuts off.

Hence, pMOS transistors only pull down to a threshold above GND, as shown in Figure  $\hat{15}(b)$ .

(a)

$$V_{DD} = V_{DD} = V_{s} = V_{DD} = V_{tn}$$

(b)

$$\sqrt[V_s]{V_s} = |V_{tp}|$$

Figure 15: Pass Transistor threshold drops

###

### <u> 1.8: NON IDEAL I-V EFFECTS</u>

\* Explain in detail about the non ideal I-V characteristics of a CMOS device. (MAY 2013)

- ÷ Explain channel length modulation and body effect. (Nov 2009, May 2013)

MOS characteristics degrade with temperature. It is useful to have a qualitative understanding of non ideal effects to predict their impact on circuit behavior.

#### (i) Mobility Degradation and Velocity Saturation:

Current is proportional to the lateral electric field  $E_{lat} = V_{ds}/L$  between source and drain.

A high voltage at the gate of the transistor attracts the carriers to the edge of the channel, causing carriers collision with the oxide interface that slows the carriers. This is called mobility degradation.

Carriers approach a maximum velocity ( $v_{sat}$ ) when high fields are applied. This phenomenon is called velocity saturation.

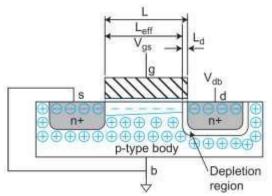

#### (ii) **Channel Length Modulation:**

Current Ids is an independent of Vds for a transistor in saturation.

The p-n junction between the drain and body forms a depletion region with a width Ld that increases with Vdb, as shown in Figure 16.

The depletion region effectively shortens the channel length to Leff = L - Ld

To avoid the body voltage into calculations, assume the source voltage is close to the body voltage i.e  $V_{db}$  = Vds.

Hence, increasing Vds decreases the effective channel length.

Shorter channel length results in higher current. Thus, Ids increases with Vds in saturation, as shown in Figure 16.

Figure 16: Depletion region shortens effective channel length

In Saturation region, Ids is

$$I_{ds} = 2 V_{GT}^{2} \left( \downarrow_{A} + V_{V}^{ds} \right)$$

$\checkmark$

Hence,  $V_A$  is proportional to channel length. This channel length modulation model is a gross oversimplification of nonlinear behavior.

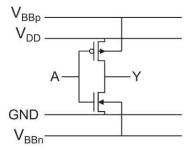

(iii) Threshold Voltage  $(V_t)$  Effects

# Explain in detail about effect and its effect in MOS device. (May 2016)

Threshold voltage  $V_t$  increases with the source voltage, decreases with the body voltage, decreases with the drain voltage and increases with channel length.

### **Body Effect:**

When a voltage  $V_{sb}$  is applied between the source and body, it increases the amount of charge required to invert the channel. Hence, it increases the threshold voltage.

The threshold voltage can be modeled as

$$V_t = V_{t0} + \gamma \left( \sqrt{\phi_s + V_{sb}} - \sqrt{\phi_s} \right)$$

where  $V_{t0}$  is the threshold voltage when the source is at the body potential,  $\phi_s$  is the surface potential at threshold and  $\gamma$  is the body effect coefficient.

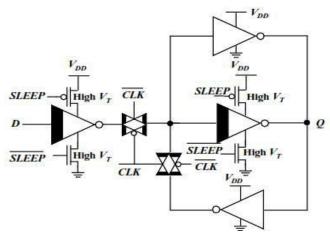

### (iv) Leakage:

Even when transistors are OFF, transistors leak small amounts of current.

Leakage mechanisms include subthreshold conduction between source and drain, gate leakage from the gate to body and junction leakage from source to body and drain to body.

Subthreshold conduction is caused by thermal emission of carriers over the potential barrier set by the threshold.

Gate leakage is a quantum-mechanical effect caused by tunneling through the extremely thin gate dielectric.

Junction leakage is caused by current through the p-n junction between the source/drain diffusions and the body.

### 1.9: Device models:

### Explain the following: Device models and device characteristics. (MAY 2014)

$\checkmark$

SPICE (Simulation Program with Integrated Circuit Emphasis) provides a wide variety of MOS transistor models with various trade-offs between complexity and accuracy.

Level 1 and Level 3 models were important, but they are no longer adequate to accurately model very small modern transistors.

BSIM models are more accurate and are presently the most widely used.

### i.Level 1 model:

I

The SPICE Level 1, or Shichman-Hodges Model is closely related to the Shockley model, enhanced with channel length modulation and the body effect.

The basic current model is:

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{t} & \text{cutoff} \\ \text{KP}\frac{W_{\text{eff}}}{L_{\text{eff}}} \left(1 + \text{LAMBDA} \times V_{ds}\right) \left(V_{gs} - V_{t} - \frac{V_{ds}}{2}\right) V_{ds} & V_{ds} < V_{gs} - V_{t} & \text{linear} \\ \frac{\text{KP}}{2}\frac{W_{\text{eff}}}{L_{\text{eff}}} \left(1 + \text{LAMBDA} \times V_{ds}\right) \left(V_{gs} - V_{t}\right)^{2} & V_{ds} > V_{gs} - V_{t} & \text{saturation} \end{cases}$$

$\checkmark$

The parameters from the SPICE model are given in ALL CAPS.

$\beta$  is written instead as KP (Weff /Leff ), where KP is a model parameter. Weff and Leff are the effective width and length.

The LAMBDA term (LAMBDA =  $1/V_A$ ) models channel length modulation.

The threshold voltage is modulated by the source-to-body voltage Vsb through the body effect.

For non negative  $V_{sb}$ , the threshold voltage,  $V_t$  is

$$V_{I} = \text{VTO} + \text{GAMMA}\left(\sqrt{\text{PHI} + V_{sb}} - \sqrt{\text{PHI}}\right)$$

Where, VTO is the "zero-bias" threshold voltage Vto,

GAMMA is the body effect coefficient, and PHI is the surface potential.

Level 1 model is easy to correlate with hand analysis, but it is too simplistic for modern design.

### ii. Level 2 and 3 models

The SPICE Level 2 and 3 models add effects of velocity saturation, mobility degradation, subthreshold conduction and drain-induced barrier lowering.

The Level 2 model is based on the Grove-Frohman equations.

Level 3 model is based on empirical equations that provide similar accuracy, faster simulation times and better convergence.

These models are not efficient models for measuring I-V characteristics of modern transistors.

#### iii. BSIM models

The Berkeley Short-Channel IGFET Model (BSIM) is a very elaborate model that is now widely used in circuit simulation.

The models are derived from the fundamental device physics but uses many number of parameters to fit the behavior of modern transistors.

- BSIM versions 1, 2, 3v3, and 4 are implemented as SPICE levels 13, 39, 49, and 54, respectively.

- BSIM is quite good for digital circuit simulation.

- Features of the model are

- Continuous and differentiable I-V characteristics across subthreshold, linear and saturation regions for good convergence.

- Sensitivity of parameters such as Vt to transistor length and width.

- Detailed threshold voltage model including body effect and drain-induced barrier Lowering (DIBL).

- Velocity saturation, mobility degradation and other short-channel effects.

- Multiple gate capacitance models.

- Diffusion capacitance and resistance models.

- Gate leakage models.

### 1.10: SCALING

### Discuss the scaling principles and its limits. (MAY 2013, Nov 2017)

Discuss the principle of constant field and lateral scaling. Write the effects of the above scaling methods on the device characteristics. (Nov 2012, Dec 2011, Nov 2015, May 2016)

Explain need of scaling, scaling principles and fundamental units of CMOS inverter. (May 2017)

#### $\checkmark$

\*

•

In VLSI design, the transistor size has reduced by 30% every two to three years. Scaling is reducing feature size of transistor.

Nowadays, transistors become smaller, switch faster, dissipate less power and cheaper.

Designers need to predict the effect of feature size scaling on chip performance to plan future products and ensure existing products for cost reduction.

$\checkmark$

Dennard's Scaling Law predicts that the basic operational characteristics of a MOS transistor can be preserved and the performance can be improved.

- Parameters of a device are scaled by a dimensionless factor S.

- These parameters include the following:

- All dimensions (in the x, y, and z directions)

- Device voltages

- Doping concentration densities

- $\checkmark$

In constant field scaling, electric fields remain the same as both voltage and distance shrink.

1/S scaling is applied to all dimensions, device voltages and concentration densities.

- Ids per transistor are scaled by 1/S.

- No. of transistors per unit area is scaled by  $S^2$ .

- Current density is scaled by S and power density remains constant.

$$\circ$$

e.g.,  $(\overline{S}^{1} + S^{1}) + S^{2}$

#### Lateral scaling (gate-shrink):

Another approach is **lateral scaling**, in which only the gate length is scaled.

This is commonly called as gate shrink, because it can be done easily to an existing mask database for a design.

- Ids per transistor are scaled by S.

- No. of transistors per unit area is scaled by S.

- Current density is scaled by  $S^2$  and power density is scaled by  $S^2$ .

- The industry generally scales process generations with 30% shrink.

- It reduces the cost (area) of a transistor by a factor of two.

A 5% gate shrink (S = 1.05) is commonly applied as a process, becomes mature to boost the speed of components in that process.

#### $\checkmark$

**Constant voltage scaling (Fixed scaling)** offers quadratic delay improvement as well as cost reduction.

It is also maintaining continuity in I/O voltage standards. Constant voltage scaling increases the electric fields in devices.

- Ids per transistor are scaled by S.

- No. of transistors per unit area is scaled by  $S^2$ .

- Current density is scaled by  $S^3$  and power density is scaled by  $S^3$ .

A 30% shrink with Dennard scaling improves clock frequency by 40% and cuts power consumption per gate by a factor of 2.

$\checkmark$

Maintaining a constant field has the further benefit, that many nonlinear factors and wear out mechanisms are unaffected.

$\checkmark$

From 90nm generation technology, voltage scaling is dramatically slowed down due to leakage. This may ultimately limit CMOS scaling.

| Parameter                                            | Sensitivity       | Dennard<br>Scaling | Constant<br>Voltage | Lateral<br>Scaling |

|------------------------------------------------------|-------------------|--------------------|---------------------|--------------------|

|                                                      | Scaling Parameter |                    |                     |                    |

| Length: L                                            |                   | 1/S                | 1/8                 | 1/S                |

| Width: W                                             |                   | 1/S                | 1/S                 | 1                  |

| Gate oxide thickness: tox                            |                   | 1/8                | 1/S                 | 1                  |

| Supply voltage: VDD                                  |                   | 1/8                | 1                   | 1                  |

| Threshold voltage: V <sub>to</sub> , V <sub>to</sub> |                   | 1/S                | 1                   | 1                  |

| Substrate doping: $N_A$                              |                   | S                  | S                   | 1                  |

Table: Influence of scaling on MOS device characteristics

### Interconnecting Scaling:

- Wires to be scaled equally in width and thickness to maintain an aspect ratio close to 2.

- Wires can be classified as local, semiglobal and global.

- Local wires run within functional units and use the bottom layers of metal.

- Semiglobal wires run across larger blocks or cores, typically using middle layers of metal.

- Both local and semiglobal wires are scaling with feature size.

- Global wires run across the entire chip using upper levels of metal.

- Global wires do not scale with feature size. Indeed, they may get longer (by a factor of DC, on the order of 1.1) because, die size has been gradually increasing.

When wire thickness is scaled, the capacitance per unit length remains constant.

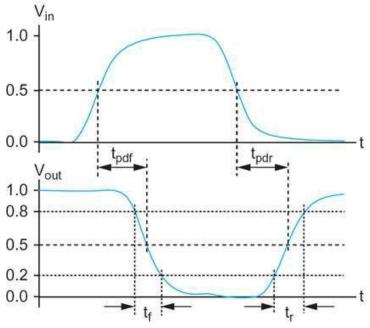

#### 1.11: Delay estimation

Derive an expression for the rise time, fall time, fall time and propagation delay of a CMOS inverter. (DEC 2013, APRIL-2015)

Important definitions for delay estimation:

### Propagation delay time (tpd):

Propagation delay time is defined as maximum time from the input crossing 50% to the output crossing 50%.

#### Contamination delay time (tcd):

Contamination delay time is defined as minimum time from the input crossing 50% to the output crossing 50%.

#### Rise time (tr):

Rise time is defined as time for a waveform to rise from 20% to 80% of its steady-state value

#### Fall time (tr):

Fall time is defined as time for a waveform to fall from 80% to 20% of its steady-state value

Edge rate is average of rise and fall time, (trf) = (tr + tf)/2

#### Delay estimation response curve:

When an input changes, the output will retain its old value for at least the contamination delay and take on its new value in, at most the propagation delay.

- Delays for the output rising is  $t_{pdr}/t_{cdr}$  and the output falling is  $t_{pdf}/t_{cdf}$ .

- Rise/fall times are also called as slopes or edge rates.

Propagation and contamination delay times are also called as max-time and min-time respectively.

Figure: Delay estimation of CMOS inverter

- The gate that charges or discharges a node is called the driver. The gates and wires being driven, are called the load. Propagation delay is usually called as delay.

- Arrival times and propagation delays are defined separately for rising and falling transitions.

- The delay of a gate may be different from different inputs. Earliest arrival times can also be computed based on contamination delays.

Expression of delay for rising output is tPLH = 0.69 Rp.CL

Where, RP – effective resistance of pMOS transistor

CL - load capacitance of CMOS inverter.

- Expression of delay for falling output is tPHL = 0.69 RN.CLWhere, RN - effective resistance of nMOS transistor

- Propagation delay of CMOS inverter is  $t_P = (t_{PLH} + t_{PHL}) / 2$

### <u>1.11.1:</u> RC Delay Model:

Discuss in detail about the resistive and capacitive delay estimation of a CMOS inverter circuit. (MAY 2013) (or) Briefly explain about the RC delay model.

$\checkmark$

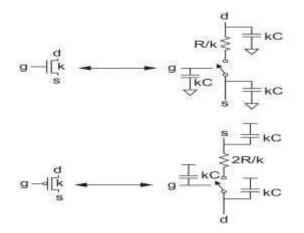

RC delay model approximates the nonlinear transistor I-V and C-V characteristics with an average resistance and capacitance over the switching range of the gate.

### Effective Resistance:

The RC delay model treats a transistor as a switch in series with a resistor.

The effective resistance is the ratio of Vds to Ids.

A unit nMOS transistor is defined to have effective resistance R.

An nMOS transistor of k times unit width has resistance R/k, because it delivers k times as much current.

A unit pMOS transistor has greater resistance, generally in the range of 2R-3R, because of its lower mobility.

According to the long-channel model, current decreases linearly with channel length (L) and hence resistance is proportional to L.

### Gate and Diffusion Capacitance:

Each transistor has gate and diffusion capacitance.

- C is the gate capacitance of a unit transistor. A transistor of k times unit width has capacitance kC.

- Diffusion capacitance depends on the size of the source/drain region.

$\checkmark$

Wider transistors have proportionally greater diffusion capacitance. Increasing channel length, increases gate capacitance proportionally but does not affect diffusion capacitance.

### Equivalent RC Circuits:

$\checkmark$

Figure shows equivalent RC circuit models for nMOS and pMOS transistors of width k with contacted diffusion on both source and drain.

$\checkmark$

The pMOS transistor has approximately twice the resistance of the nMOS transistor, because holes have lower mobility than electrons.

#### EC6601-VLSI DESIGN

Figure: RC model of nMOS &pMOS transistors

1.12: Stick diagram

### Explain about stick diagram in VLSI design. (April 2008)

$\checkmark$

A stick diagram is a cartoon of a chip layout. A "stick diagram" is a paper and pencil tool that use to plan the layout of a cell.

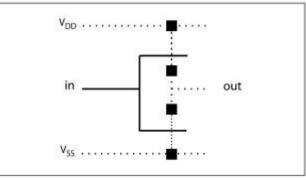

The stick diagram resembles the actual layout, but uses "sticks" or lines to represent the devices and conductors. Figure 17, shows a stick diagram for an inverter.

$\checkmark$

The stick diagram represents the rectangles with lines, which represent wires and component symbols.

The stick diagram does not represent all the details of a layout, but it makes some relationship much clearer and it is simple to draw.

Layouts are constructed from rectangles, but stick diagrams are built from cartoon symbols for components and wires.

#### Stick diagram Rules:

$\checkmark$

**Rule 1:** When two or more 'sticks' of the same type cross or touch each other, that represents electrical contact.

$\checkmark$

**Rule 2:** When two or more 'sticks' of the different type cross or touch each other, there is no electrical contact. If electrical contact is needed, we have to show the connection explicitly.

$\checkmark$

**Rule 3:** When a poly crosses diffusion, it represents a transistor. If a contact is shown, then it is not a transistor. A transistor exists where a polysilicon (red) stick crosses either an n-diffusion (green) stick or a p-diffusion (yellow) stick.

$\checkmark$

**Rule 4:** In CMOS, a demarcation line is drawn to avoid touching of p-diff with n-diff. All pMOS must lie on one side of the line and all nMOS will have to be on the other side.

Figure 17: Stick diagram for an inverter

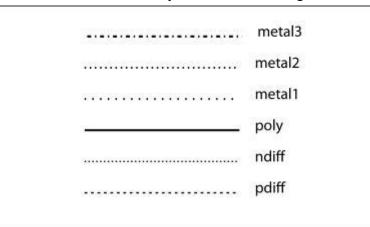

The symbols for wires used on various layers are shown in Figure 18.

Figure 18: Symbols for wires used on various layers

**Drawing stick diagrams in color**: Red for poly, green for n-diffusion, yellow for p-diffusion, and shades of blue for metal are typical colors.

A few simple rules for constructing wires from straight-line segments ensure that, the stick diagram corresponds to a feasible layout.

$\checkmark$

Wires cannot be drawn at arbitrary angles. Only horizontal and vertical wire segments are allowed.

Two wire segments on the same layer, which cross are electrically connected.

Vias to connect wires, which do not normally interact, are drawn as black dots.

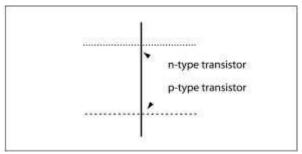

- Figure 19, shows the stick figures for transistors.

- Each type of transistor is represented as poly and diffusion crossings, much as in the layout.

Figure 19: Stick figures for transistors

Area and aspect ratio are also difficult to estimate from stick diagrams.

Stick diagrams are especially important tools for layouts built from large cells and for testing the connections between cells.

### Example:

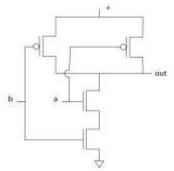

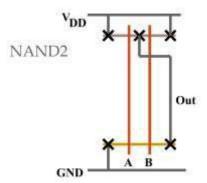

Here is the transistor schematic for a two-input NAND gate:

And here is a stick diagram for the two-input NAND:

### 1.13: Layout Design Rules

Draw and explain briefly the n-well CMOS design rules. (NOV 2007, April 2008, MAY 2014)

- Discuss in detail with a neatlayout, the design rules for a CMOS inverter.

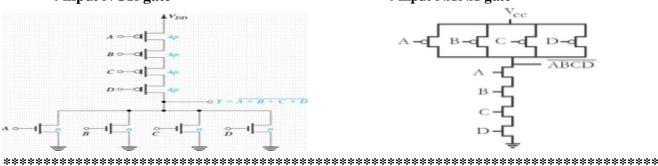

- Write the layout design rules and draw diagram for four input NAND and NOR. (Nov 2016)

Layout rules also referred to as **design rules**.

- It can be considered as prescription for preparing the photomasks, which are used in the fabrication of integrated circuits.

- The rules are defined in terms of feature sizes (widths), separations and overlaps.

- The main objective of the layout rules is to build reliable functional circuits in as small area as possible.

Layout design rules describe how small features can be and how closely they can be reliably packed in a particular manufacturing process.

Design rules are a set of geometrical specifications that dictate the design of the layout masks.

- A design rule set provides numerical values for minimum dimensions and line spacing.

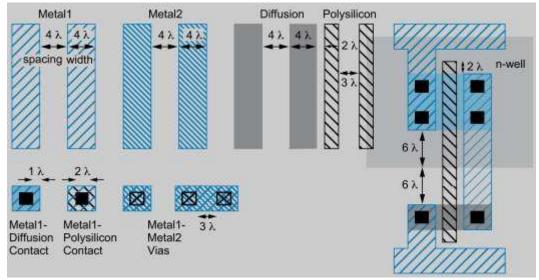

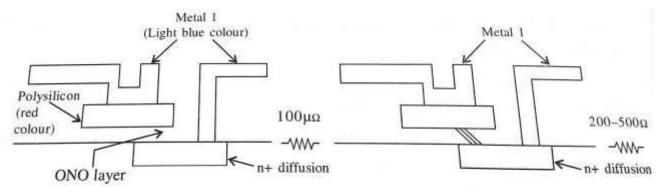

- Scalable design rules are based on a single parameter ( $\lambda$ ), which characterizes the resolution of the process.  $\lambda$  is generally half of the minimum drawn transistor channel length.

- This length is the distance between the source and drain of a transistor and is set by the minimum width of a polysilic on wire.

#### Lambda based rule (Scalable design rule):

Lambda-based rules are round up dimensions of scaling to an integer multiple of  $\lambda$ .

- Lambda rules make scaling layout small. The same layout can be moved to a new process, simply by specifying a new value of  $\lambda$ .

- The minimum feature size of a technology is characterized as  $2\lambda$ .

- The MOSIS rules are expressed in terms of lambda.

- These rules allow some degree of scaling between processes.

- Only need to reduce the value of lambda and the designs will be valid in the next process down in size.

- These processes rarely shrink uniformly.

- Thus, industry usually uses the actual micron design rules for layouts.

- There are set of micron design rules for a hypothetical 65 nm process.

- We can observe that, these rules differ slightly but not immensely from lambda based rules with lambda = 0.035 micro meter.

- Upper level metal rules are highly variable depending on the metal thickness. Thicker wires require greater widths, spacing and bigger vias.

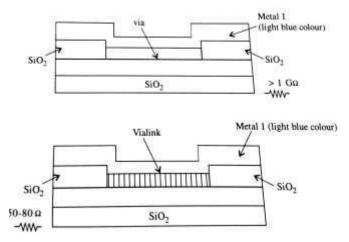

- Two metal layers in an n-well process has the following:

- Metal and diffusion have minimum width and spacing of 4  $\lambda$ .

- Contacts are  $2\lambda \times 2\lambda$  and must be surrounded by  $1\lambda$  on the layers above and below.

- Polysilicon uses a width of 2  $\lambda$ .

- Polysilicon overlaps diffusion by 2  $\lambda$  where a transistor is desired and has a spacing of 1  $\lambda$  away where no transistor is desired.

- Polysilicon and contacts have spacing of 3  $\lambda$  from other polysilicon or contacts.

- N-well surrounds pMOS transistors by 6  $\lambda$  and avoids nMOS transistors by 6  $\lambda$ .

Figure: Simplified  $\lambda$  -based design rules with CMOS inverter layout diagram

## Design Rule:

### Well Rules:

- The n-well is usually a deeper implant than the transistor source/drain implants.

- Therefore, it is necessary to provide sufficient clearance between the n-well edges and the adjacent n+ diffusions.

### **Transistor Rules:**

CMOS transistors are generally defined by at least four physical masks.

There are active (also called diffusion, diff, thinox, OD, or RX), n-select (also called n-implant, n-imp, or nplus), p-select (also called p-implant, pimp, or pplus) and polysilicon (also called poly, polyg, PO, or PC).

The active mask defines all areas, where n- or p-type diffusion is to be placed *or* where the gates of transistor are to be placed.

### **Contact Rules:**

There are several generally available contacts:

- Metal to p-active (p-diffusion)

- Metal to n-active (n-diffusion)

- Metal to polysilicon

- Metal to well or substrate

### **Metal Rules:**

Metal spacing may vary with the width of the metal line.

Metal wire width of minimum spacing may be increased. This is due to etch characteristics versus large metal wires.

$\checkmark$

\*\*

Processes may allow vias to be placed over polysilicon and diffusion regions.

Some processes allow vias to be placed within these areas, but do not allow the vias to the boundary of polysilicon or diffusion.

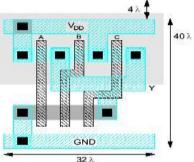

- Horizontal N-diffusion and p-diffusion strips

- Vertical polysilicon gates

- Metall VDD rail at top

- Metall GND rail at bottom

Draw diagram for four input NAND and NOR gate. (Nov 2017) 4 input NOR gate 4 input NANA gate

### 1.14: Latchup problem:

Discuss the orgin of latch up problems in CMOS circuits with necessary diagrams. Explain the remedial measures. (Nov 2007, April 2008)

- A CMOS process is slowed down by developing low-resistance paths between VDD and GND, causing catastrophic meltdown. The phenomenon is called latchup.

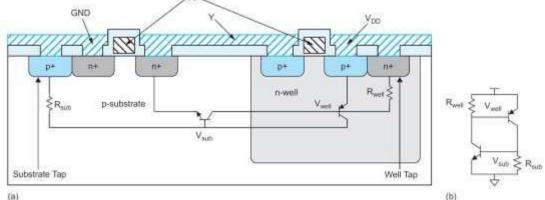

- Latchup problem arises when parasitic bipolar transistors are formed by the substrate, well and diffusion.

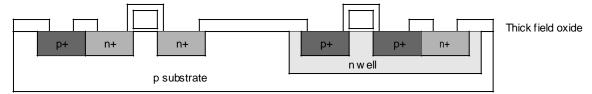

- The cause of the latchup effect can be understood by examining the process cross-section of a CMOS inverter, as shown in Figure (a).

- The schematic shows, a circuit composed of an npn-transistor, a pnp-transistor, and two resistors connected between the power and ground rails (Figure (b)).

(a

The npn transistor is formed between the grounded n-diffusion source of the nMOS transistor, the p-type substrate and the n-well.

The resistors are due to the resistance through the substrate or well to the nearest substrate and well taps.

The cross-coupled transistors form a bistable silicon-controlled rectifier (SCR). Both parasitic bipolar transistors are OFF.

Latchup can be triggered, when transient currents flow through the substrate during normal chip power-up.

$\checkmark$

÷

Latchup prevention is easily accomplished by

- Minimizing Rsub and Rwell.

- Use of guard rings

SOI process avoids latchup entirely, because they have no parasitic bipolar structures.

### 1.15: Process parameters for MOS and CMOS: CMOS TECHNOLOGIES:

The four main CMOS technologies are

n-Well process p-Well process Twintub Process

Silicon on Insulator

Explain the different steps involved in n-well CMOS fabrication process with neat diagrams. (Nov 2007, Nov 2009, Nov 2016)

Describe with neat diagram the n-well and channel formation in CMOS process. (Nov/Dec 2014)(Nov/Dec 2011) (April/May 2011) (Nov/Dec 2012)

SiO<sub>2</sub>

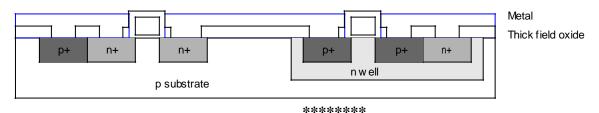

### n-WELL PROCESS:

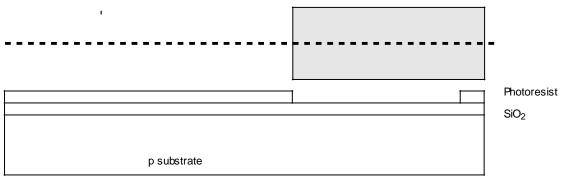

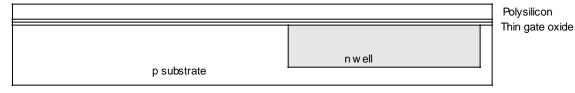

### Step 1: Start with blank wafer

First step will be to form the n-well

- Cover wafer with protective layer of SiO<sub>2</sub> (oxide)

- Remove layer where n-well should be built.

psubstnate

### Step 2: Oxidation

Grow SiO<sub>2</sub> on top of Si wafer, at  $900 - 1200^{\circ}$  C with H<sub>2</sub>O or O<sub>2</sub> in oxidation furnace.

p substrate

### Step 3: Photoresist

- Spin on photoresist

- Photoresist is a light-sensitive organic polymer.

- Softens, where exposed to light.

p substrate Photoresist

### Step 4: Lithography

- Expose photoresist through n-well mask.

- Strip off exposed photoresist.

#### Step 5: Etch

- Etch oxide with hydrofluoric acid (HF).

- Only attracts oxide, where resist has been exposed.

#### **Step 6: Strip Photoresist**

• Etch the remaining photoresist using a mixture of acids.

|             | [[ | SiC | )2 |

|-------------|----|-----|----|

|             |    |     | 2  |

|             |    |     |    |

| p substrate |    |     |    |

|             | 27 |     |    |

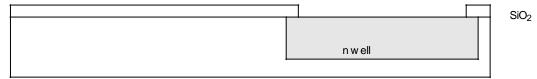

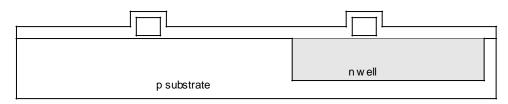

### Step 7: n-well

n-well is formed with diffusion or ion implantation.

### Step 8: Strip Oxide

- Strip off the remaining oxide using HF.

- Back to bare wafer with n-well.

- Subsequent steps involve similar series of steps.

n w ell

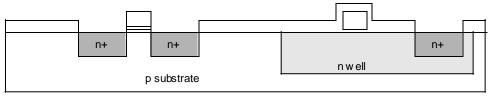

#### Step 9:Polysilicon

• Deposit thin layer of oxide. Use CVD to form poly and dope heavily to increase conductivity.

### Step 10: Polysilicon Patterning

• Use same lithography process to pattern polysilicon.

### **Step 11: Self-Aligned Process**

Cover with oxide to define n diffusion regions.

#### Step 12: N-diffusion

- Pattern oxide, using n+ active mask to define n diffusion regions.

- Diffusion or ion implantation is used to create n diffusion regions.

UNIT-I EC6601-VLSI DESIGN

Step 13:

• Strip off oxide to complete patterning step.

n+

n+

n+

n well

n+

n+

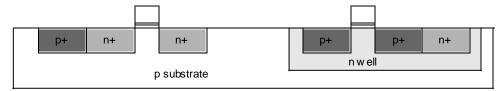

### Step 14:P-Diffusion

• Similar set of steps are followed to form p+ diffusion regions for pMOS source and drain and substrate contact.

### **Step 15: Contacts**

- Now, we need to wire together the devices.

- Cover chip with thick field oxide.

- Etch oxide, where contact cuts are needed.

### Step 16: Metallization

- Sputter on aluminum over whole wafer.

- Pattern to remove excess metal, leaving wires.

### **P-WELL PROCESS:**

• A common approach to p-well CMOS fabrication is to start with moderately doped n-type substrate (wafer), create the p-type well for the n-channel devices and build the p-channel transistor in the native n-substrate.

### \*

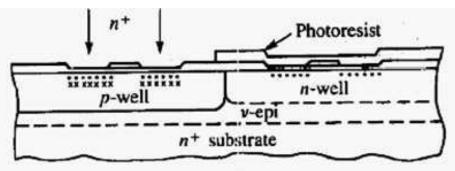

Explain the twin tub process with a neat diagram. (Nov 2007, April 2008) Twintub process:

### Step 1:

n- Substrate is taken initially, which is shown in figure.

### Step 2:

Next step is epitaxial layer deposition. Lightly doped epitaxial layer is deposited above n-substrate.

#### UNIT-I DESIGN

### Step 3:

The next step is tub formation. Two wells are formed namely n-well and p-well. Polysilicon layer is formed above overall substrate.

### Step 4:

Polysilicon gates are formed for n-well and p-well by using photo-etching process. **Step 5:**

$n^+$ diffusion is formed in n-well,  $P^+$  diffusion is formed in p-well. These are used for VDD contact and Vss contact. These are known as substrate formation.

### Step 6:

\*

Then, contact cuts are defined as in n-well process. Then metallization is processed.

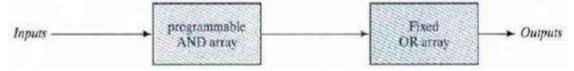

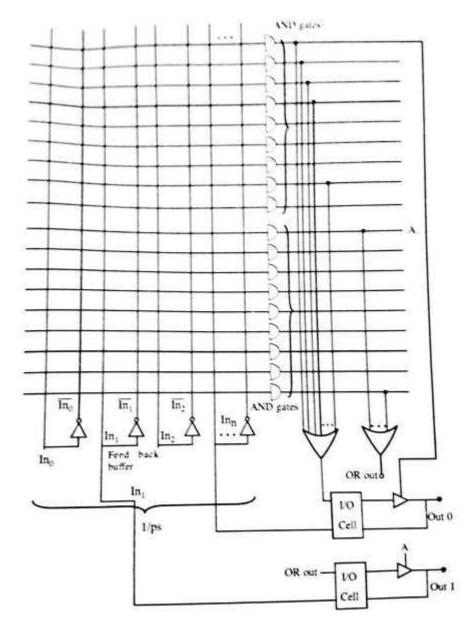

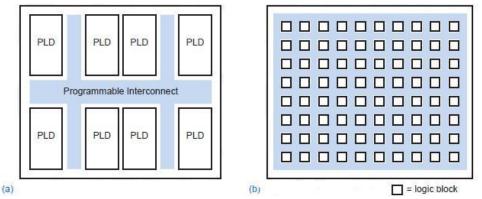

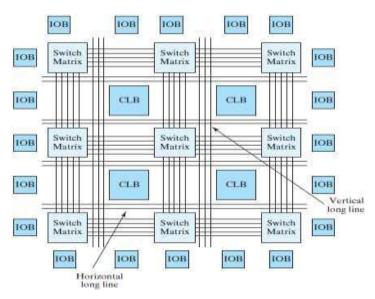

### **UNIT II - COMBINATIONAL LOGIC CIRCUITS**

Examples of Combinational Logic Design, Elmore's constant, Pass transistor Logic, Transmission gates, static and dynamic CMOS design, Power dissipation – Low power design principles.

### 2.1:Introduction (Combinational Logic Circuit):

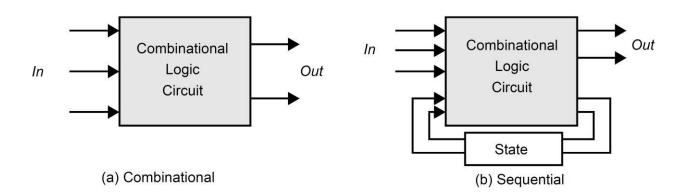

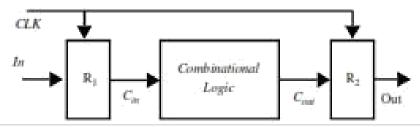

- Digital logics are divided into combinational and sequential circuits.

- Combinational circuits are circuits where outputs depend only on the present inputs.

- For sequential or regenerative circuit, the output is not only a function of the current input data, but also of previous values of the input signals.

- A sequential circuit includes a combinational logic portion and a memory module that holds the state. Example are registers, counters and memory.

- The building blocks for combinational circuits are logic gates, while the building blocks for sequential circuits are registers and latches.

- The delay of a logic gate depends on its output current I, load capacitance C and output voltage swing V.

- Alternative (ratioed circuits, dynamic circuits and pass transistor circuits) CMOS logic configurations are called circuit families.

- nMOS transistors provide more current than pMOS for the same size and capacitance, so nMOS networks are preferred.

### Examples of combinational circuits

(i) CMOS inverter:

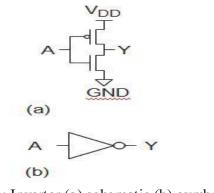

Figure: Inverter (a) schematic (b) symbol Y = A

#### EC6601-VLSI DESIGN

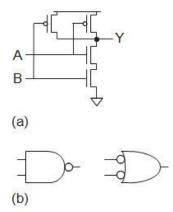

(ii) Two input NAND gate:

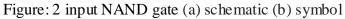

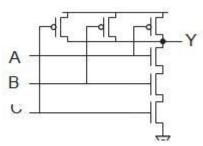

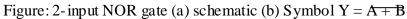

(iii) Three input NAND gate:

Figure: 3 –input NAND gate Schematic Y=A.B.C

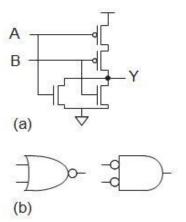

(iv) Two input NOR gate:

\*\*\*\*\*\*\*

### Example:

Sketch a static CMOS gate computing  $Y = (\overline{A + B + C}) \cdot \overline{D}$ .

### 2.2: Circuit Families

Briefly discuss about the classification of circuit families and comparison of the circuit families. (May 2014, APRIL-2015)

### Draw and explain the function of static CMOS.

### 2.2.1: Static CMOS

• Static CMOS circuits with complementary nMOS pulldown and pMOS pullup networks are used for the majority of logic gates in integrated circuits.

Figure: Static CMOS inverter

### Advantages of static CMOS:

- Static CMOS circuits have good noise margins

- Static CMOS circuits are fast, low power, easy to design.

- Static CMOS circuits are widely supported by CAD tools.

- Static CMOS circuits are available in standard cell libraries.

### Drawback of static CMOS

- It requires both nMOS and pMOS transistors for each input.

- It has a relatively large logical effort.

- Gate delay is

### increased. a. Bubble pushing

- CMOS stages are inherently inverting, so AND and OR functions must be built from NAND and NOR gates.

- DeMorgan's law helps with this conversion:

$$\overline{A.B} = \overline{A} + \overline{B}$$

$$\overline{A+B} = \overline{A.B}$$

Figure: Bubble pushing with DeMorgan's law

- A NAND gate is equivalent to an OR of inverted inputs.

- A NOR gate is equivalent to an AND of inverted inputs.

- The same relationship applies to gates with more inputs.

- Switching between these representations is easy and is often called bubble pushing.

### b. Compound Gates

- Static CMOS also efficiently handles compound gates computing various inverting combinations of AND/OR functions in a single stage.

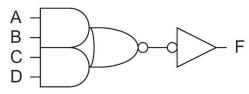

- The function F = AB + CD can be computed with an AND-OR INVERT- 22 (AOI22) gate and an inverter, as shown in Figure.

Figure: Logic using AOI22 gate

- Logical effort of compound gates can be different for different inputs.

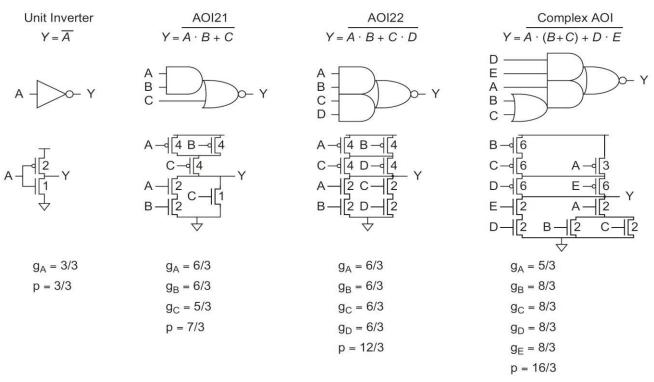

- Figure shows, how logical efforts can be estimated for the AOI21, AOI22 and a more complex compound AOI gate.

Figure: Logical efforts and parasitic delays of AOI gates

### c. Input ordering delay effect

- The logical effort and parasitic delay of different gate inputs are different.

- Consider the falling output transition occurring, when one input hold a stable 1 value and the other rises from 0 to 1.

- If input B rises last, node x will initially be at  $V_{DD} V_t = V_{DD}$ , because it was pulled up through the nMOS transistor on input A.

- The Elmore delay is  $(R/2)(2C) + R(6C) = 7RC = 2.33 \tau$

- If input A raises last, node x will initially be at 0 V, because it was discharged through the nMOS transistor on input B.

- No charge must be delivered to node x, so the Elmore delay is simply  $R(6C) = 6RC = 2\tau$ .

Figure: 2 – input NAND gate Schematic Y=A.B

- We define the outer input to be the input closer to the supply rail (e.g., B) and the inner input to be the input closer to the output (e.g., A).

- Therefore, if one signal is known to arrive later than the others, the gate is faster when that signal is connected to the inner input.

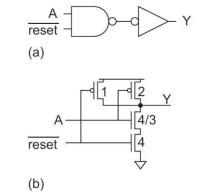

### d. Asymmetric gates

- When one input is far less critical than another, even symmetric gates can be made asymmetric to favor the late input at the expense of the early one.

- In a series network, this involves connecting the early input to the outer transistor and making the transistor wider, so that, it offers less series resistance when the critical input arrives.

- In a parallel network, the early input is connected to a narrower transistor to reduce the parasitic capacitance.

- Consider the path in Figure (a). Under ordinary conditions, the path acts as a buffer between A and Y.

- When reset is asserted, the path forces the output low.

- If reset only occurs under exceptional circumstances and take place slowly, the circuit should be optimized for input-to-output delay at the expense of reset.

- This can be done with the asymmetric NAND gate in Figure (b).

Figure: Resettable buffer optimized for data input

#### EC6601-VLSI DESIGN

#### e. Skewed gates

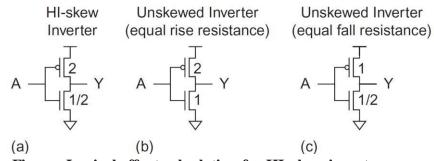

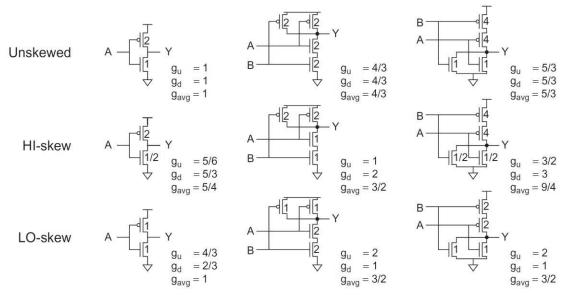

#### What is meant by skewed gate and give functions of skewed gate with schematic diagrams?

- One input transition is more important than the other. HI-skew gates to favor the rising output transition. LO-skew gates to favor the falling output transition.

- This favoring can be done by decreasing the size of the noncritical transistor.

- The logical efforts for the rising (up) and falling (down) transitions are called g<sub>u</sub> and g<sub>d</sub>, respectively.

- Figure (a) shows, how a HI-skew inverter is constructed by downsizing the nMOS transistor.

- This maintains the same effective resistance for the critical transition, while reducing the input capacitance relative to the unskewed inverter of Figure (b).

- Thus reducing the logical effort on that critical transition to  $g_u = 2.5/3 = 5/6$ .

- The logical effort for the falling transition is estimated by comparing the inverter to a smaller unskewed inverter with equal pulldown current, shown in Figure (c), giving a logical effort of  $g_d = 2.5/1.5 = 5/3$ .

Figure: Logical effort calculation for HI-skew inverter

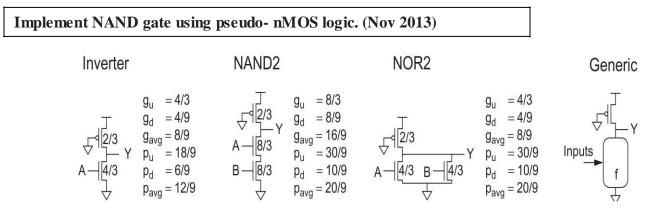

NAND2

• Figure shows, HI skew and LO-skew gates with a skew factor of two. Skewed gates are sometimes denoted with an H or an L on their symbol in a schematic.

Inverter

NOR2

Figure: List of skewed gates

#### UNIT-II

# f. P/N ratios

- By accepting a slower rise delay, the pMOS transistors can be downsized to reduce input capacitance and average delay significantly.

- P/N ratio is defined as the ratio of pMOS to nMOS transistor width. For processes, a mobility ratio of  $\mu n/\mu p = 2$ .

# g. Multiple threshold voltages

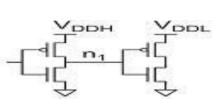

- Some CMOS processes offer two or more threshold voltages.

- Transistors with lower threshold voltages produce more ON current, but also leak exponentially more OFF current.

- Libraries can provide both high- and low-threshold versions of gates.

- The low-threshold gates can be used carefully to reduce the delay of critical paths.

- Skewed gates can use low-threshold devices on, only the critical network of transistors.

# 2.3: Elmore's Delay

What is meant by Elmore's delay and give expression for Elmore's delay?

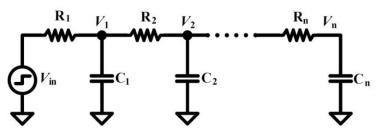

• The Elmore delay model estimates the delay from a source, switching to one of the leaf nodes. Delay is the sum over each node i of the capacitance C<sub>1</sub> on the node multiplied by the effective resistance R.

Propagation delay time :

$$t_{pd} \approx \sum_{\substack{n \text{ odes } i \\ n \text{ odes } i}} R_{i - to -source} C_{i}$$

=  $R_1 C_1 + (R_1 + R_2) C_2 + ... + (R_1 + R_2 + ... + R_N) C_N$

- Delay of an ideal fanout-of-1 inverter with no parasitic capacitance is  $\tau = 3RC$ .

- The normalized delay *d* relative to this inverter delay:

$$d = \frac{t_{pd}}{\tau}$$

Figure: RC delay equivalent for series of transistors

#### Linear delay model

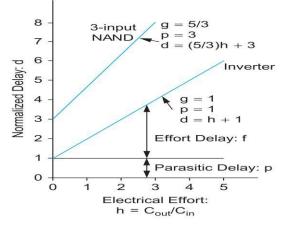

- The RC delay model is one, where delay is a linear function of the fanout of a gate.

- The normalized delay of a gate can be expressed in units of Y as d = f + p. Where p is the parasitic delay inherent to the gate when no load is attached.

- f is the effort delay or stage effort that depends on the complexity.

- Effort delay of the gate is f = gh.

Where g is the logical effort (An inverter has a logical effort of 1).

- Logical effort is defined as the ratio of the input capacitance of a gate to the input capacitance of an inverter delivering the same output current.

- h is the fanout or electrical effort. Electrical effort is defined as ratio of the output capacitance to input capacitance.

- More complex gates have greater logical efforts, indicating that they take longer time to drive a given fanout.

- For example, the logical effort of the 3-input NAND gate is 5/3.

- The electrical effort can be computed as  $h = \frac{a_{4L}}{C}$

Where  $C_{out}$  is the capacitance of the external load being driven and  $C_{in}$  is the capacitance of the gate.

- Normalized delay vs electrical effort for an idealized inverter and 3-input NAND gate shown in diagram.

- The y-intercepts indicate the parasitic delay. The slope of the lines is the logical effort.

- The inverter has a slope of 1. The NAND gate has a slope of 5/3.

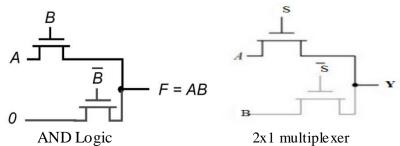

#### 2.4: Pass Transistor circuits:

#### Explain Pass transistor logic with neat sketches. (April 2008)

- In pass-transistor circuits, inputs are applied to the source/drain diffusion terminals.

- These circuits build switches using either nMOS pass transistors or parallel pairs of nMOS and pMOS transistors called as transmission gates.

#### UNIT-II

#### EC6601-VLSI DESIGN

- The nMOS transistors pass "0" well but 1" poorly. Figure (a) shows an nMOS transistor with the gate and drain tied to  $V_{DD}$ .

- Initially at Vs = 0.  $V_{gs} > V_{tn}$ , so the transistor is ON and current flows.

- Therefore, nMOS transistors attempting to pass a 1 never pull the source above  $V_{DD} V_{tn}$ . This loss is called a threshold drop.

- The pMOS transistors pass 1"s well but 0"s poorly.

- If the pMOS source drops below  $|V_{tp}|$ , the transistor cuts off.

- Hence, pMOS transistors only pull down to a threshold above GND, as shown in Figure (b).

(a)

$$V_{DD} = V_s = V_{DD} - V_{tn}$$

Figure : Pass Transistor threshold drops

• Figures show an implementation of the AND function and 2x1 multiplexer using only NMOS transistors.

- In AND gate, if the *B* input is high, the top transistor is turned ON and copies the input *A* to the output *F*.

- When *B* is low, the bottom pass transistor is turned ON and passes a 0.

- In 2x1 multiplexer, if the S selection input is high, the top transistor is turned ON and allows input *A* to the output Y.

- When *S* is low, the bottom pass transistor is turned ON and passes the B input.

- An NMOS device is effective at passing a 0 but is poor at pulling a node to  $V_{DD}$ . When the pass transistor pulls a node high, the output only charges up to  $V_{DD} V_{tn}$ .

# **Application:**

• Pass transistors are essential to the design of efficient 6-transistor static RAM cells used in modern systems.

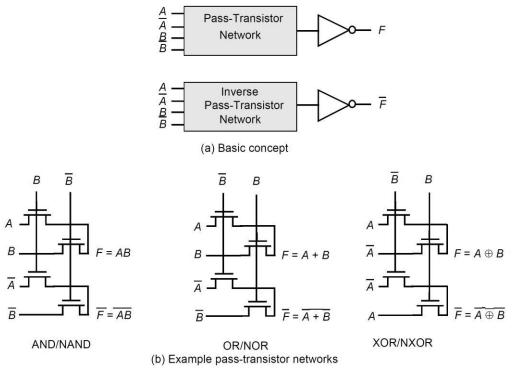

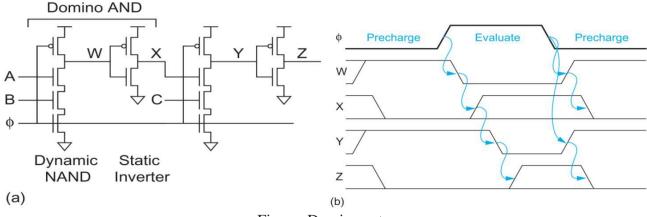

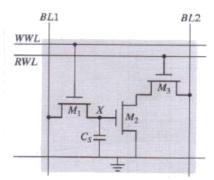

# 2.4.1: Differential Pass Transistor Logic

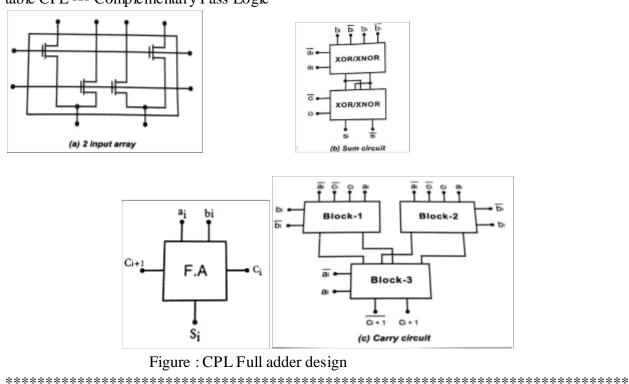

- For high performance design, a differential pass-transistor logic family, called CPL or DPL, is commonly used.

- The basic idea is to accept true and complementary inputs and produce true and complementary outputs.

- A number of CPL gates (AND/NAND, OR/NOR, and XOR/NXOR) are shown in Figure.

- Since the circuits are *differential*, complementary data inputs and outputs are always available.

- Both polarities of every signal eliminate the need for extra inverters, as is often the case in static CMOS or pseudo-NMOS.

- CPL belongs to the class of *static* gates, because the output-defining nodes are always connected to either  $V_{DD}$  or GND through a low resistance path.

- This is advantage for the noise flexibility.

Figure: Complementary pass-transistor logic (CPL).

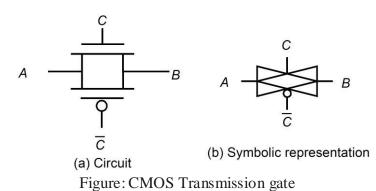

# 2.4.2: CMOS with transmission gates

Discuss in detail the characteristics of CMOS Transmission gates.(May 2016, May 2017, Nov 2017)

Explain Transmission gates with neat sketches. (April 2008)

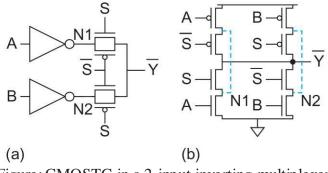

- A transmission gate in conjunction with simple static CMOS logic is called CMOS with transmission gate.

- A transmission gate is parallel pairs of nMOS and pMOS transistor.

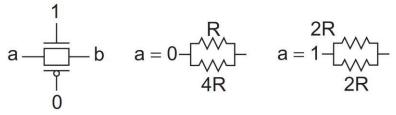

- A single nMOS or pMOS pass transistor suffers from a threshold drop.

- Transmission gates solve the threshold drop but require two transistors in parallel.

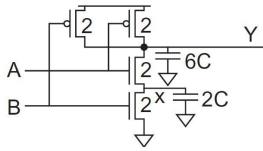

- The resistance of a unit-sized transmission gate can be estimated as R for the purpose of delay estimation.

- Current flow the parallel combination of the nMOS and pMOS transistors. One of the transistors is passing the value well and the other is passing it poorly.

- A logic-1 is passed well through the pMOS but poorly through the nMOS.

- Estimate the effective resistance of a unit transistor passing a value in its poor direction as twice the usual value: 2R for nMOS and 4R for pMOS.

- The given below figure shows the parallel combination of resistances. When passing a 0, the resistance is  $R \parallel 4R = (4/5)R$ .

- The effective resistance passing a 1 is  $2R \parallel 2R = R$ .

- Hence, a transmission gate made from unit transistors is approximately R in either direction.

- Transmission gates are built using equal-sized nMOS and pMOS transistors.

- Boosting the size of the pMOS transistor only slightly improves the effective resistance while significantly increasing the capacitance.

Figure: Effective resistance of a unit transmission gate

• Figure (a) redraws the multiplexer to include the Inverters that drive the diffusion inputs but to exclude the output inverter. Figure (b) shows this multiplexer drawn at the transistor level.

Figure: CMOSTG in a 2-input inverting multiplexer

# 2.5: Static CMOS design:

# 2.5.1:Ratioed Circuits:

# Write short notes on ratioed circuits. (Nov 2016)

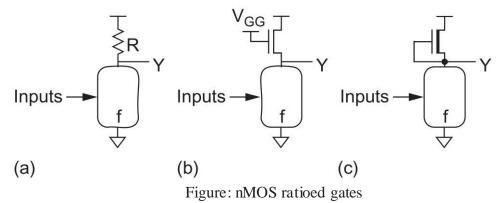

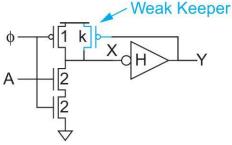

- The ratioed gate consists of an nMOS pulldown network and pullup device called the static load.

- When the pulldown network is OFF, the static load pulls the output to 1.

- When the pulldown network turns ON, it fights the static load.

- The static load must be weak enough that, the output pulls down to an acceptable 0. Hence, there is a ratio constraint between the static load and pulldown network.

Advantage: Stronger static loads produce faster rising outputs.

# **Disadvantages:**

- $\circ$  Degrade the noise margin and burn more static power when the output is 0.

- A resistor is a simple static load, but large resistors consume a large layout area in typical MOS processes.

- Another technique is to use an nMOS transistor with the gate tied to  $V_{GG}$  (Shown in fig.(b)). If  $V_{GG} = V_{DD}$ , the nMOS transistor will only pull up to  $V_{DD} - V_t$ .

- Figure (c) shows depletion load ratioed circuit.

# 2.5.2: pseudo nMOS

# Explain the detail about pseudo-nMOS gates with neat circuit diagram. (April/May 2011) (Nov/Dec 2013)

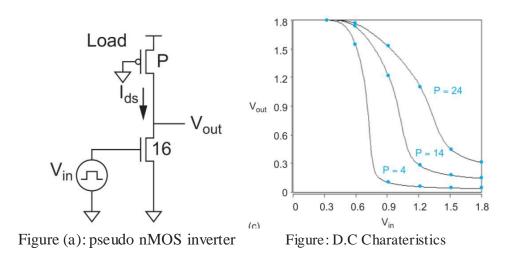

- Figure (a) shows a pseudo-nMOS inverter.

- The static load is built from a single pMOS transistor that has its gate grounded, so it is always ON.

- The beta ratio affects the shape of the transfer characteristics and the  $V_{OL}$  of the inverter.

- Larger relative pMOS transistor size offer faster rise time, but less sharp transfer characteristics.

- **Drawback:** Pseudo-nMOS gates will not operate correctly if  $V_{OL} > V_{IL}$  of the receiving gate.

• Figure shows several pseudo-nMOS logic gates.

Figure: Pseudo-nMOS logic gates

# 2.5.3: Ganged capacitor:

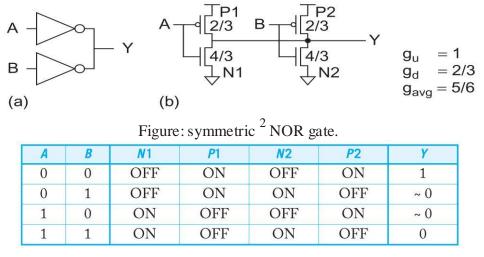

- Figure shows pairs of CMOS inverters ganged together.

- The truth table is given in Table, showing that the pair compute the NOR function. Such a circuit is sometimes called a symmetric <sup>2</sup> NOR, or ganged CMOS.

Table: Operation of symmetric NOR

- When one input is 0 and the other 1, the gate can be viewed as a pseudo-nMOS circuit with appropriate ratio constraints.

- When both inputs are 0, both pMOS transistors turn on in parallel, pulling the output high faster than they would, in an ordinary pseudo nMOS gate.

- When both inputs are 1, both pMOS transistors turn OFF, saving static power dissipation.

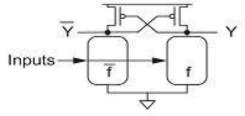

# 2.5.4: Cascode voltage switch logic

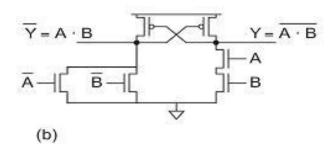

# Explain about DCVSL logic with suitable example. (May 2017)

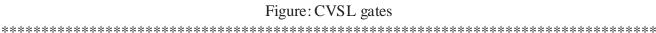

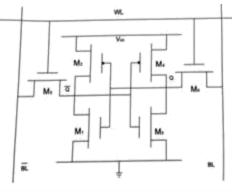

- Cascode Voltage Switch Logic (CVSL) seeks the benefits of ratioed circuits without the static power consumption.

- It uses both true and complementary input signals and computes both true and complementary outputs using a pair of nMOS pulldown networks, as shown in Figure (a).

- The pulldown network f implements the logic function as in a static CMOS gate, while *f* uses inverted inputs feeding transistors arranged in the conduction complement.

- For any given input pattern, one of the pulldown networks will be ON and the other OFF.

- The pulldown network that is ON will pull that output low.

- This low output turns ON the pMOS transistor to pull the opposite output high.

- When the opposite output rises, the other pMOS transistor turns OFF, so no static power dissipation occurs.

- Figure (b) shows a CVSL AND/NAND gate.

# Advantage:

• CVSL has a potential speed advantage because all of the logic is performed with nMOS transistors, thus reducing the input capacitance.

(a)

# 2.6:Dynamic CMOS design:

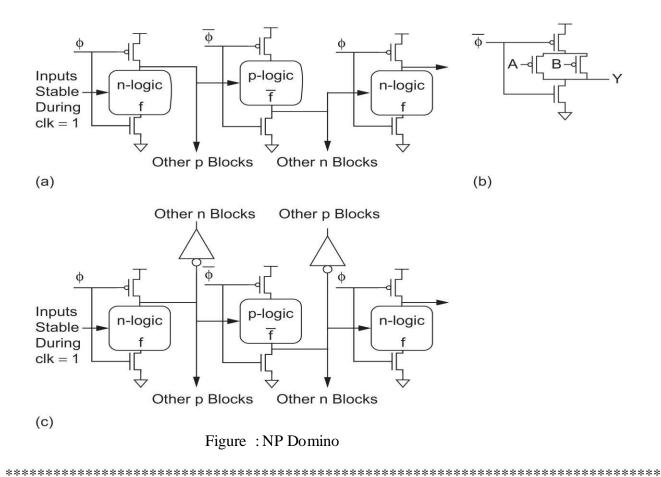

Describe the basic principle of operation of dynamic CMOS, domino and NP domino logic with neat diagrams. (NOV 2011)

# **Dynamic Circuits:**

# Write short notes on Dynamic CMOS circuits. (Nov 2016)

- Ratioed circuits reduce the input capacitance by replacing the pMOS transistors connected to the inputs with a single resistive pullup.

- The drawbacks of ratioed circuits include

- Slow rising transitions,

- Contention on the falling transitions,

- $\circ$  Static power dissipation and a nonzero V<sub>OL</sub>.

- Dynamic circuits avoid these drawbacks by using a clocked pullup transistor rather than a pMOS that is always ON.

- Figure compares (a) static CMOS, (b) pseudo-nMOS, and (c) dynamic inverters.

Figure: Comparison of (a) static CMOS, (b) pseudo-nMOS, and (c) dynamic inverters

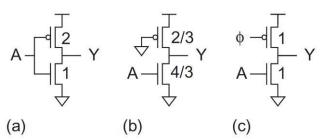

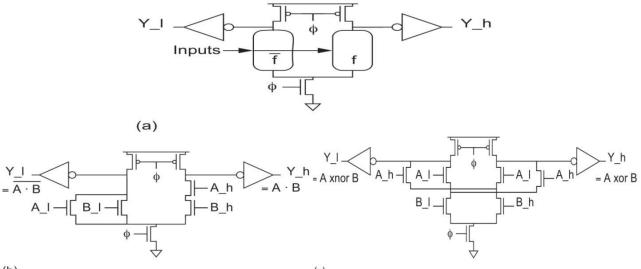

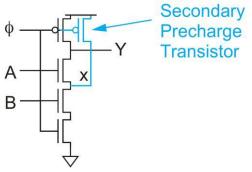

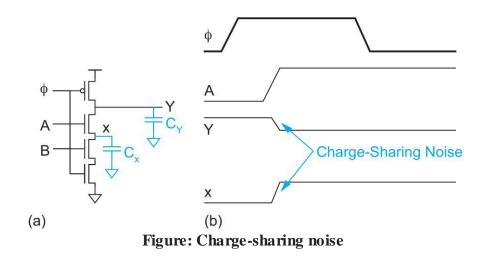

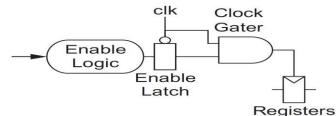

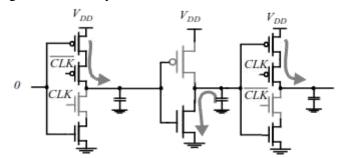

Dynamic circuit operation is divided into two modes, as shown in Figure.

(i) During precharge, the clock φ is 0, so the clocked pMOS is ON and initializes the output Y

high.

(ii) During evaluation, the clock is 1 and the clocked pMOS turns OFF. The output may remain high or may be discharged low through the pulldown network.

Figure: Precharge and evaluation of dynamic gates

# Advantages:

- Dynamic circuits are the fastest used circuit family because they have lower input capacitance and no contention during switching.

- Zero static power dissipation.

# **Disadvantags:**

• They require careful clocking, consume significant dynamic power and are sensitive to noise during evaluation mode.

#### UNIT-II

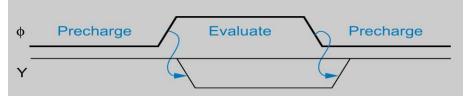

# Foot transistor:

- In Figure (c), if the input A is 1 during precharge, contention will take place because both the pMOS and nMOS transistors will be ON.

- When the input cannot be guaranteed to be 0 during precharge, an extra clocked evaluation transistor can be added to the bottom of the nMOS stack.

- To avoid contention as shown in the below figure, extra transistor is sometimes called as foot is added.

Figure: Footed dynamic inverter

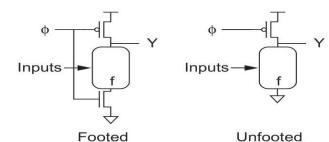

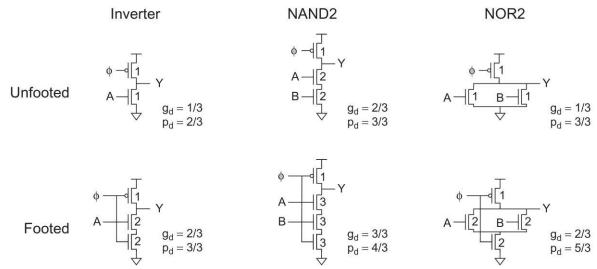

• The given below figure shows generic footed and unfooted gates.

Figure: Generalized footed and unfooted dynamic gates

• The given below figure estimates the falling logical effort of both footed and unfooted dynamic gates.

# Figure: List of dynamic gates

- The pull down transistor's width is chosen to give unit resistance. Precharge occurs while the gate is idle and takes place more slowly.

- Therefore, the precharge transistor width is chosen for twice unit resistance.

- This reduces the capacitive load on the clock and the parasitic capacitance at the expense of greater rising delays.

- Footed gates have higher logical effort than their unfooted concept but are still an improvement over static logic.

- The parasitic delay does increase with the number of inputs, because there is more diffusion capacitance on the output node.

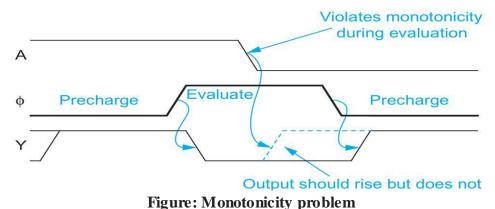

- A fundamental difficulty with dynamic circuits is the monotonicity requirement. While a dynamic gate is in evaluation, the inputs must be monotonically rising.

- That is, the input can start LOW and remain LOW, start LOW and rise HIGH, start HIGH and remain HIGH, but not start HIGH and fall LOW.

- Figure shows waveforms for a footed dynamic inverter in which the input violates monotonicity.

- During precharge, the output is pulled HIGH.

- When the clock rises, the input is HIGH, so the output is discharged LOW through the pulldown network.

- The input later falls LOW, turning off the pulldown network. However, the precharge transistor is also OFF, so the output floats, staying LOW rather than rising.

- The output will remain low until the next precharge step.

- The inputs must be monotonically rising for the dynamic gate to compute the correct function.

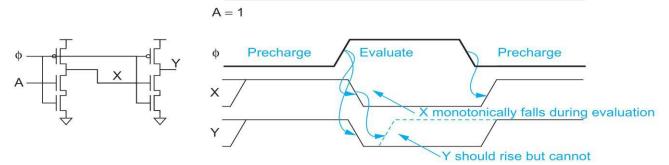

- Unfortunately, the output of a dynamic gate begins HIGH and monotonically falls LOW during evaluation.

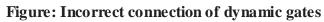

- This monotonically falling output X is not a suitable input to a second dynamic gate expecting monotonically rising signals, as shown in the below figure.

- Dynamic gates sharing the same clock cannot be directly connected.

- This problem is often overcome with domino logic.

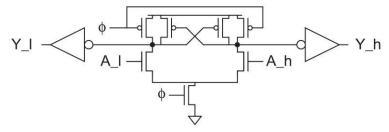

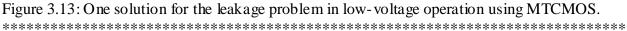

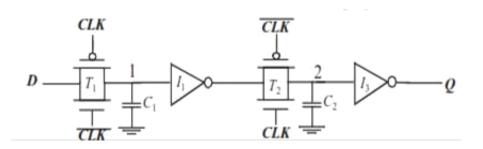

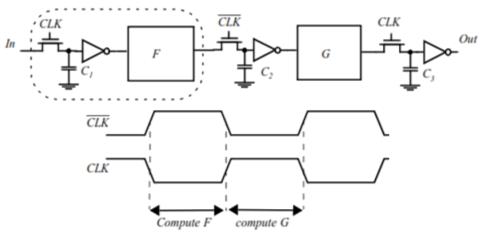

# <u>2.6.1: Domino logic</u>

# Explain the domino logic families with neat diagrams. (NOV 2012, APRIL-2015, Nov 2017)

- The dynamic-static pair together is called a domino gate.

- The monotonicity problem can be solved by placing a static CMOS inverter between dynamic gates, as shown in figure (a).

- This converts the monotonically falling output into a monotonically rising signal suitable for the next gate, as shown in figure (b).

- A single clock can be used to precharge and evaluate all the logic gates within the chain.

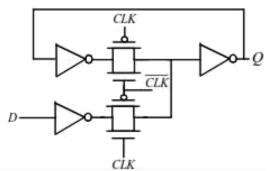

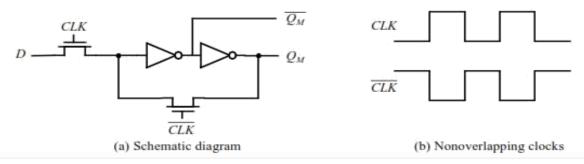

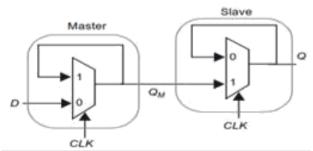

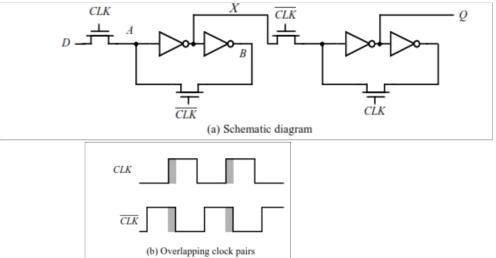

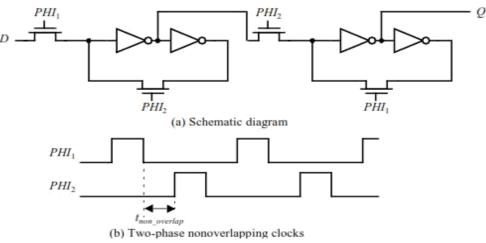

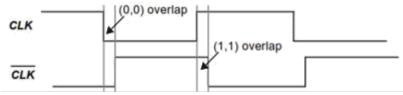

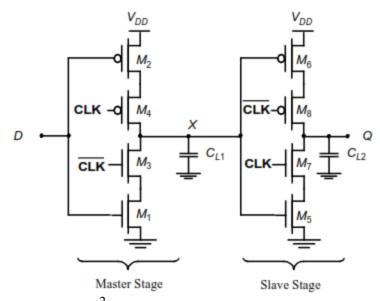

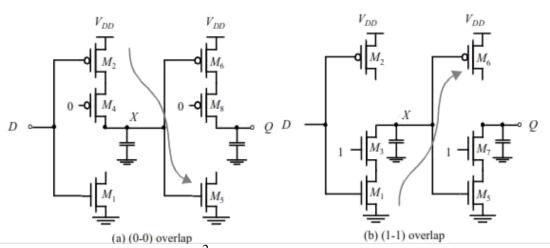

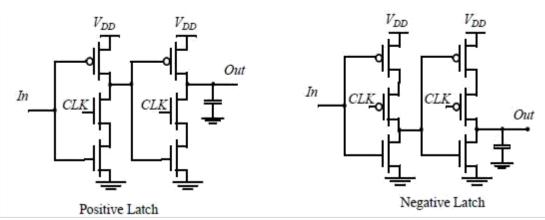

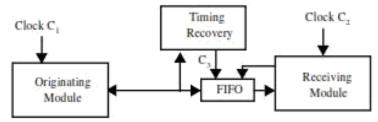

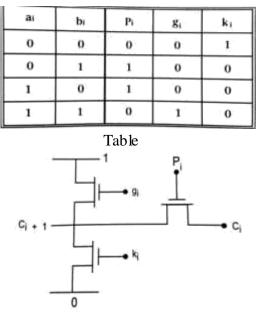

- The dynamic output is monotonically falling during evaluation, so the static inverter output is monotonically rising.